1.4 Características NMOS

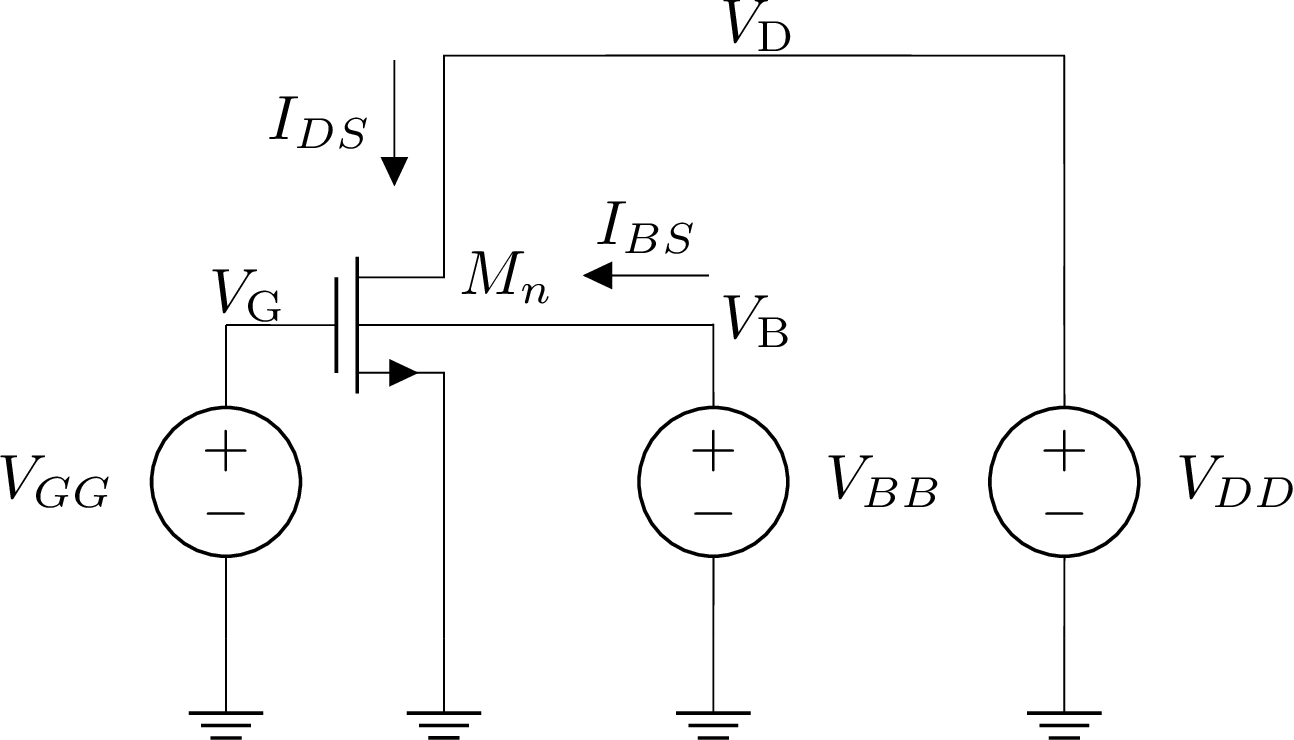

O circuito da Figura 1.9 é que foi usado para a caracterização dos transistores NMOS, tanto de \(1\ \mu m\) quanto \(50\ nm\). A diferença para uma e outra tecnologia é o valor das tensões máximas. Para \(1\ \mu m\), temos \(V_{DD}=5\ V\). Para \(50\ nm\), temos \(V_{DD}=1\ V\). O mesmo vale para os limites de \(V_{GS}\).

Figura 1.9: Circuito de caracterização de um NMOS.

1.4.1 Dependência com \(V_{GS}\), parâmetro \(V_{DS}\), \(L=1\ \mu m\)

Figura 1.10: \(I_{DS}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.11: \({g_{m}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.12: \(g_{{m}_{b}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.13: \({r_{o}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.14: \(V_{{DS}_{sat}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

1.4.2 Dependência com \(V_{GS}\), parâmetro \(V_{DS}\), \(L=50\ nm\)

Figura 1.15: \(I_{DS}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.16: \({g_{m}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.17: \(g_{{m}_{b}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.18: \({r_{o}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.19: \(V_{{DS}_{sat}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

1.4.3 Dependência com \(V_{DS}\), parâmetro \(V_{GS}\), \(L=1\ \mu m\)

Figura 1.20: \(I_{DS}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.21: \({g_{m}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.22: \(g_{{m}_{b}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.23: \({r_{o}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.24: \(V_{{DS}_{sat}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

1.4.4 Dependência com \(V_{DS}\), parâmetro \(V_{GS}\), \(L=50\ nm\)

Figura 1.25: \(I_{DS}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.26: \({g_{m}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.27: \(g_{{m}_{b}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.28: \({r_{o}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

Figura 1.29: \(V_{{DS}_{sat}}\ \text{vs. }V_{GS}\text{, param.: }V_{DS}.\)

1.4.5 Códigos de Simulação

Código de simulação (NGSpice) para o NMOS: \(1\ \mu m\), Parâmetro: \(V_{GS}\)

*** Capítulo 1

** Autor: Patrick Mendes dos Santos

** Caracterização do NMOS - 1u - R. J. Baker

** VBS: zero

*** Opcoes

.options savecurrents

.options filetype=ascii

.temp 25

.include ../modelos/cmosedu_models.txt

*** Circuito

**Componentes

* Usando o modelo de R. J. Baker

mn d g 0 b N_1u l={2*lambda} w={20*lambda} ad={6*lambda*wn} as={6*lambda*wn} pd={12*lambda+2*wn} ps={12*lambda+2*wn}

** Fontes

vdd d 0 dc vd

vgg g 0 dc 2

vbb b 0 dc 0

** Parametros

.param vd=5

.param lambda=500n

.param wn={20*lambda}

.end

.control

set color0=white

set color1=black

set wr_vecnames

set width = 4098

set wr_singlescale

save all @mn[id] @mn[ibs] @mn[gm] @mn[gds] @mn[gmbs] @mn[vdsat]

+@mn[cgs] @mn[cgd] @mn[cgb] @mn[cbd] @mn[cbs]

+@mn[vgs] @mn[vds] @mn[vbd] @mn[vbs]

echo "Realizando simulação variando tensão na porta Vgg."

let vdreno = 1

foreach vdreno 1 2 3 4 5

echo "Realizando simulação variando tensão na porta Vgg para Vdd igual a"$vdreno"."

alter @vdd[dc] = '$vdreno'

dc vgg 0 5 1m

let mn.id = @mn[id]

let mn.ibs = @mn[ibs]

let mn.gm = @mn[gm]

let mn.gds = @mn[gds]

let mn.gmbs = @mn[gmbs]

let mn.vsat = @mn[vdsat]

let mn.cgs = @mn[cgs]

let mn.cgd = @mn[cgd]

let mn.cgb = @mn[cgb]

let mn.cbd = @mn[cbd]

let mn.cbs = @mn[cbs]

let mn.vgs = @mn[vgs]

let mn.vds = @mn[vds]

let mn.vbd = @mn[vbd]

let mn.vbs = @mn[vbs]

set arquivo = {'carac_nmos_1u_vgg_vdd_'}{$vdreno}{'.dat'}

wrdata $arquivo mn.id mn.ibs mn.gm mn.gds mn.gmbs mn.vsat

+mn.cgs mn.cgd mn.cgb mn.cbd mn.cbs

+mn.vgs mn.vds mn.vbd mn.vbs

end

.endcCódigo de simulação (NGSpice) para o NMOS: \(50 nm\), Parâmetro: \(V_{GS}\)

*** Capítulo 1

** Autor: Patrick Mendes dos Santos

** Caracterização do NMOS - 50n - R. J. Baker

** VBS: zero

*** Opcoes

.options savecurrents

.options filetype=ascii

.temp 25

.include ../modelos/cmosedu_models.txt

*** Circuito

**Componentes

* Usando o modelo de R. J. Baker

mn d g 0 b N_50n l={2*lambda} w={20*lambda} ad={6*lambda*wn} as={6*lambda*wn} pd={12*lambda+2*wn} ps={12*lambda+2*wn}

** Fontes

vdd d 0 dc vd

vgg g 0 dc 0.5

vbb b 0 dc 0

** Parametros

.param vd=1

.param lambda=50n

.param wn={20*lambda}

.end

.control

set color0=white

set color1=black

set wr_vecnames

set width = 4098

set wr_singlescale

save all @mn[id] @mn[ibs] @mn[gm] @mn[gds] @mn[gmbs] @mn[vdsat] @mn[vth]

+@mn[cgs] @mn[cgd] @mn[cgb] @mn[cbd] @mn[cbs]

+@mn[cdd] @mn[cgg] @mn[css] @mn[cbb] @mn[capbd] @mn[capbs]

+@mn[vgs] @mn[vds] @mn[vbs]

echo "Realizando simulação variando tensão na porta Vgg."

let vdreno = 1

foreach vdreno 0.2 0.4 0.6 0.8 1

echo "Realizando simulação variando tensão na porta Vgg para Vdd igual a"$vdreno"."

alter @vdd[dc] = '$vdreno'

dc vgg 0 1 0.2m

let mn.id = @mn[id]

let mn.ibs = @mn[ibs]

let mn.gm = @mn[gm]

let mn.gds = @mn[gds]

let mn.gmbs = @mn[gmbs]

let mn.vsat = @mn[vdsat]

let mn.vth = @mn[vth]

let mn.cgs = @mn[cgs]

let mn.cgd = @mn[cgd]

let mn.cgb = @mn[cgb]

let mn.cbd = @mn[cbd]

let mn.cbs = @mn[cbs]

let mn.cdd = @mn[cdd]

let mn.cgg = @mn[cgg]

let mn.css = @mn[css]

let mn.cbb = @mn[cbb]

let mn.capbd = @mn[capbd]

let mn.capbs = @mn[capbs]

let mn.vgs = @mn[vgs]

let mn.vds = @mn[vds]

let mn.vbs = @mn[vbs]

set arquivo = {'carac_nmos_50n_vgg_vdd_'}{$vdreno}{'.dat'}

wrdata $arquivo mn.id mn.ibs mn.gm mn.gds mn.gmbs mn.vsat mn.vth

+mn.cgs mn.cgd mn.cgb mn.cbd mn.cbs

+mn.cdd mn.cgg mn.css mn.cbb mn.capbd mn.capbs

+mn.vgs mn.vds mn.vbs

end

.endc