A 龙芯CPU设计与体系结构教学实验系统

龙芯CPU设计与体系结构教学实验系统的核心是一块基于FPGA芯片的嵌入式系统开发板(以下简称“开发板”),箱内的其他器件包括:开发板配套的电源适配器1个、JTAG下载线和适配器1套以及串口线1根。下面简要介绍开发板的硬件设计方案和时钟设计方案。如果想详细了解开发板,请参阅提供的开发板原理图。

A.1 开发板的硬件设计方案

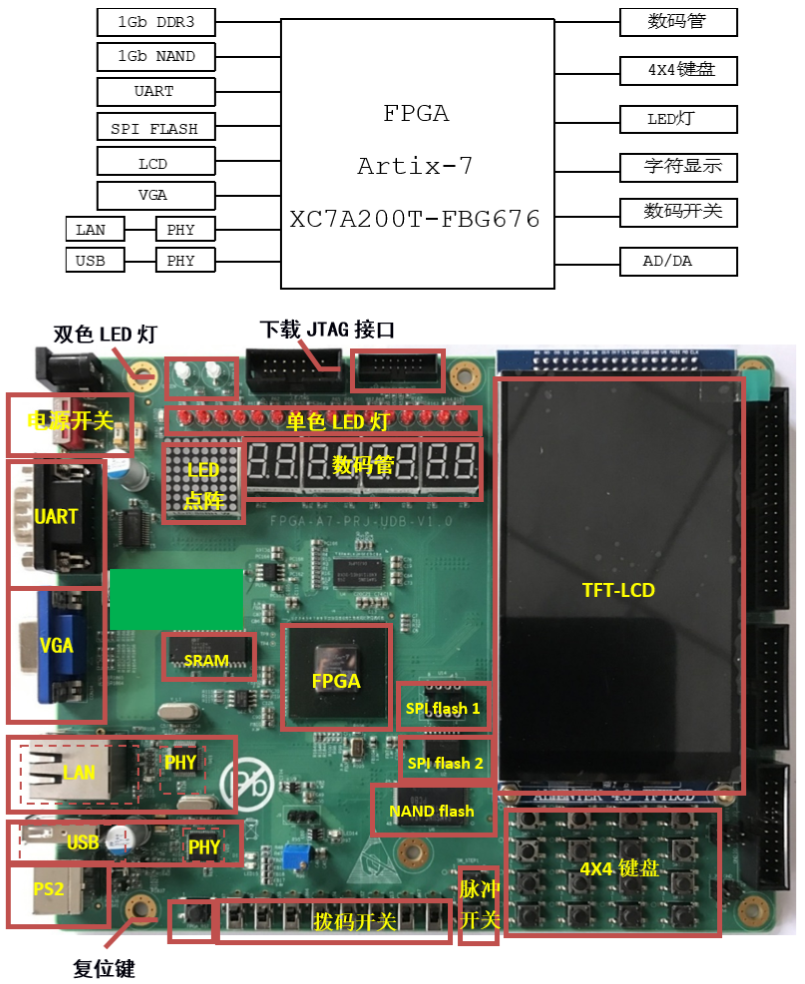

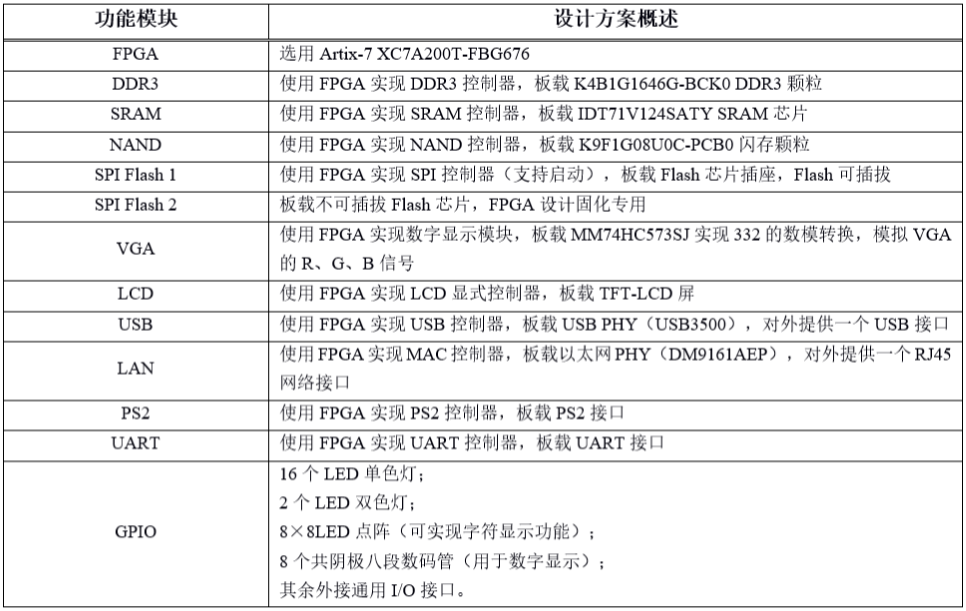

图A.1分别给出了开发板的逻辑结构示意图和实物图,可以对照两幅图来加强感性认识。开发板的主要部分的设计方案如图A.2中列表所示。

图 A.1: 开发板的逻辑结构和实物图

图 A.2: 开发板主要部分的设计方案

A.2 开发板原理图

当使用开发板完成实验时,也就是使用Vivado工具进行电路实现时,需要将设计的电路顶层的input/output接口信号绑定到开发板上FPGA芯片的I/O引脚上,该绑定关系由Vivado工程中的约束文件(*.xdc)指定。

因此,在使用Vivado工具进行电路实现时,需要编写约束文件,此时需要查找开发板原理图以确定引脚编号。我们整理了开发板上常用的I/O设备的引脚列表,如LED灯、数码管等,参见本书资源中的“引脚对应关系.xlsx”。

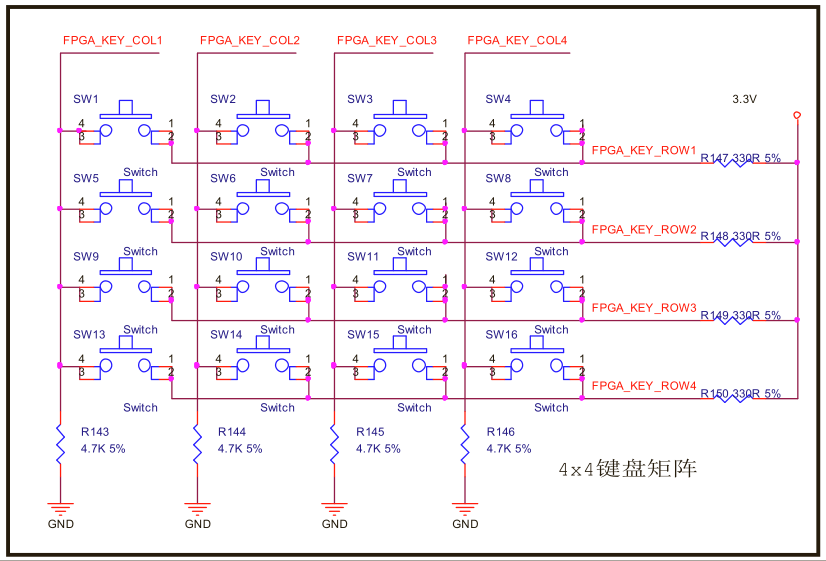

比如,假设电路实现中使用4×4矩阵键盘,现在需要确定矩阵键盘的接口。我们可以直接从“引脚对应关系.xlsx”文件中获得矩阵键盘引脚对应的FPGA芯片的I/O编号,也可以查看原理图得到对应的编号。4×4矩阵键盘原理图如图A.3所示。

图 A.3: 4X4矩阵键盘原理图

可以看到,4×4键盘矩阵只用了8个引脚:FPGA_KEY_COL_1~FPGA_KEY_COL_4,FPGA_KEY_ROW_1~FPGA_KEY_ROW_4。其中列FPGA_KEY_COL*通过一个高电阻接地,行FPGA_KEY_ROW*通过一个相对低的电阻接高电平。当有开关闭合时,闭合处对应的列FPGA_KEY_COL*和行FPGA_KEY_ROW*有相同的电平。

如果只需要使用同一行的按键,由于列FPGA_KEY_ROW*是默认接高电平的,因此当有按键时,相应的行FPGA_KEY_COL*会收到一个高电平,即得到一个“1”,无按键时会得到一个“0”。需要注意,检测按键时最好加上防抖功能。

当需要使用多行的按键时,就需要通过扫描方式确认按键位置了。扫描方式是从列FPGA_KEY_COL*一次输入低电平“0”,随后检测行FPGA_KEY_ROW*处得到的电平值。如果四行均为高电平“1”,则表示按键不在该列;如果有一行为低电平“0”,表示按键在该列,且在该行。

假如在电路实现时使用了键盘左上角的按键,就需要在原理图中查找行FPGA_KEY_COL_1,可以看到该列线是连接到FPGA芯片中编号为V8的I/O引脚上。

类似地,可以查找FPGA_KEY_COL_2 ~ FPGA_KEY_COL_4和FPGA_KEY_ROW_1 ~ FPGA_KEY_ROW_4对应的FPGA芯片的I/O引脚编号。