LoongArch CPU设计实验

2023-04-10

第 1 章 CPU 芯片研发过程概述

作为一本注重实战性的书籍,在开始讲述CPU设计的内容之前,我们先给大家科普一下工业界研发CPU芯片的大致过程。这部分内容可以帮助你建立对CPU的研发的认识,进而了解本书各章中讲授的技术对应真实工作中的哪个研发环节。毕竟,好的工程师不能“只见树木不见森林”。

1.1 处理器和处理器核

首先,我们需要分清楚处理器(CPU)和处理器核(CPU Core)这两个概念。在三四十年前,晶体管集成密度还没有现在这么高,一款处理器芯片的主体就是一个处理器核。随着集成电路工艺的快速演进,芯片上晶体管的集成密度越来越高。现在常见的处理器芯片不再是传统意义上的“运算器 + 控制器”,而已经是一个片上系统(System on Chip,简称SoC),处理器核只是这个片上系统的一个核心IP。

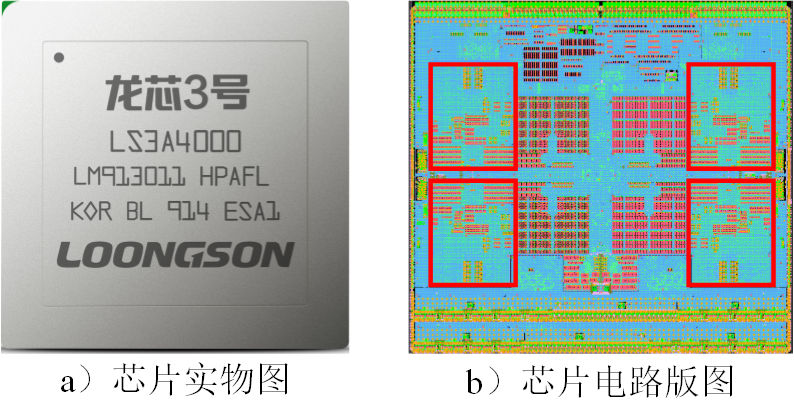

以龙芯3A4000通用处理器芯片为例,大家平时看到的芯片实物是图1.1a中的样子。芯片底部是一个有很多引脚的电路板,上面有一个塑料或金属的外壳,芯片中最核心的硅片部分被封装这个管壳中。图1.1b给出的电路版图对应的就是芯片中的硅片部分。

图 1.1: 龙芯3A4000通用处理器芯片实物图及电路版图

龙芯3A4000芯片是一款集成了四个GS464V处理器核的处理器芯片。为了方便大家查看,我们在图1.1中用矩形框将四个GS464V处理器核的位置和形状标识了出来。大家可以很清楚地看到,处理器核是处理器芯片的重要组成部分,然而一个处理器芯片中包含的并不仅仅是处理器核。对于龙芯3A4000芯片来说,除处理器核外,还包含多核共享的三级高速缓存(L3 Cache)、Hyper Transport 高速总线接口控制器和 PHY、DDR3/DDR4内存控制器和PHY以及一系列其他功能模块。

我们很难在一本书里讲清楚一款现代处理器芯片的所有设计过程。像龙芯3A4000处理器芯片中集成的DDR3/DDR4内存控制器和Hyper Transport高速总线接口控制器的设计都可以分别写成一本书。在本书中,我们关注的只是处理器芯片中的处理器核,它是处理器芯片中真正执行指令、进行运算和控制的核心。因此,在本书接下来的内容中,我们将不再严格区分“处理器”和“处理器核”这两个词。

1.2 芯片产品的研制过程

处理器芯片产品的研制过程与一般的芯片产品大致相同,通常需要经历下面五个阶段:

- 芯片定义:在芯片定义阶段,需要进行市场调研,针对客户需求制定芯片的规格定义,并进行可行性分析、论证。

- 芯片设计:芯片设计阶段的工作可以进一步划分为硅片设计和封装设计。(大家平时看到的芯片是已经将硅片封装进管壳之后的样子。)

- 芯片制造:硅片设计和封装设计完成后,将被交付到工厂,进入芯片制造阶段。芯片制造又包含掩模制造、晶圆生产和封装生产几个方面。

- 芯片封测:当晶圆和封装管壳都生产完毕后,就进入芯片封测阶段。通常需要先对晶圆进行中测(有些低成本芯片没有此环节),然后进行划片、封装,最后对封装后的芯片进行成测。中测和成测都通过后,就基本能确保这些芯片不会有生产环节引入的错误,可以对其展开最终的验证了。

- 芯片验证:在最终验证环节中,光有芯片是不够的,需要将芯片焊接到预先设计和生产好的电路板上,装配成机器并加载软件后,才能开始验证。在验证阶段,要对芯片的各个技术指标进行测评,当发现异常时,需要找到出错原因。如果是芯片设计的问题,那么就需要修正设计错误,再次进行制造、封测和验证阶段的工作。

目前在产业界,将芯片设计和制造分离已经成为主流趋势。芯片设计(Fabless)企业关注芯片定义和设计,制造和封测多采用委托外协的方式(如苹果、高通、AMD、ARM等公司)。芯片制造(Foundry)企业则聚焦于芯片的制造,它们自己不做设计,如台积电(TSMC)、中芯国际(SMIC)等公司。在这种产业分工合作体系之下,一款芯片的价值主要是由芯片的设计环节所赋予的。

1.3 芯片设计的工作阶段

对于一个CPU来说,其硅片设计的工作可进一步划分为如下9个阶段:

- 明确设计规格。

- 制定设计方案。

- 进行设计描述(编写RTL代码)。

- 功能和性能验证。

- 逻辑综合。

- 版图规划。

- 布局布线。

- 网表逻辑验证、时序检查、版图验证。

- 交付流片。

无论是硬件产品还是软件产品,设计之初必然要明确其设计规格,确定设计的边界约束情况。对于CPU设计开发来说,典型的设计规格包括支持的指令集,主频、性能、面积和功耗指标以及接口信号定义。

明确了设计规格之后,就要给出相应的设计方案。这个设计方案通常是用自然语言或高级建模语言从较为抽象的角度对CPU的微结构设计所做的行为级描述。例如,CPU划分为多少级流水、每一级流水线最多处理多少条指令、有多少个运算部件、指令的执行调度机制是什么,等等,这些内容都要在设计方案中详细地给出。

有了设计方案之后,接下来就需要将行为级描述进一步转换为EDA综合工具可以处理的RTL级描述。这个过程通常是由人完成的。近年来学术界和工业界在高层次描述向低层次描述的自动化转换方面做了很多积极的尝试,可以将一个非自然语言的行为级描述转换为HDL语言甚至直接综合为门级电路。不过就目前的技术发展来看,针对CPU设计,有经验的工程师设计出的电路质量还是远高于高层次综合工具的。由于CPU产品具有“赢者通吃”的特性,单纯地缩短上市周期并不能获得持久的商业优势,因此CPU对于电路质量的要求比领域专用加速器的要求要高得多。所以,短期来看CPU产品从设计方案到设计描述还将主要依赖人工。

寄存器传输级(Register Transfer Level,简称RTL)描述使得我们可以在这个层次展开功能和性能的验证。所谓功能和性能验证,是指证明设计的功能正确性和性能指标是否符合设计规格中的定义,它发现并修正的是设计描述阶段引入的逻辑实现错误。如果发现功能或性能上的错误,就需要返回设计描述阶段进行修改,甚至要返回设计方案阶段对不合理的地方进行修改,然后再进行功能和性能验证。在整个设计过程中,会在这几个阶段反复迭代,直至所有的功能和性能验证都通过。这里我们反复提到了“验证”这个概念,它与软件开发中的“测试”非常相似。之所以不用“测试”这个词,是因为在芯片设计制造领域“测试”这个概念另有所指。芯片设计制造领域的测试虽然也是检测电路的功能和性能是否符合设计指标,但是它发现并修正的是芯片在生产制造环节中引入的电路故障。

通过验证环节的检验,确定功能和性能指标都符合预期后,RTL级的描述将通过EDA综合工具转化成门级网表。综合工具将根据设计者给出的约束,尽力保证综合出的门级网表满足时序、面积和功耗方面的要求。

接下来的工作是对最终实现的电路版图进行设计规划,即对电路的接口引脚、各主要数据通路的相对位置关系进行平面布局规划。目前这个过程仍需要大量的人工参与。版图规划完成之后,自动布局、布线工具将读入之前综合所得的网表并生成电路的版图。

生成电路版图以后,除了要对版图自身进行设计规则检查和电路/版图一致性检查外,还需要针对最终设计进行静态时序分析和功耗分析以确保达到频率和功耗目标,同时将提取出的延迟信息反标至网表中,进行带有反标SDF的延迟和时序检查的功能仿真验证。各类验证检测无误后,就可以将版图交付给工厂进行生产。

总的来说,CPU的设计开发流程与其他类型的超大规模数字集成电路的设计开发流程基本一致。毕竟从电路的角度来看,CPU就是一种数字逻辑电路。但CPU又是一种特殊的数字逻辑电路,它在设计、实现与功能验证三个方面具有其自身的特点。对于CPU设计的初学者而言,学习的难点也常集中在这三个方面。本书后面各章将针对这三个方面展开论述。